Introduction

In the world of computing, particularly when discussing processors and system architectures, it’s essential to have an understanding of different CPU instruction sets and optimizations. One such specification you may encounter is x86_64-v3. This architecture has gained prominence due to its role in optimizing performance for modern applications on x86_64-based systems.

In this comprehensive guide, we will explore everything you need to know about the x86_64-v3 architecture. This will include its definition, its advantages, key differences from other instruction sets, its compatibility, how to enable it, and practical examples. Whether you’re a developer, system administrator, or just someone passionate about technology, this guide will equip you with essential knowledge about x86_64-v3.

What is x86_64-v3? |

x86_64-v3 is a specific CPU architecture optimization targeted at modern processors, designed to provide better performance over previous versions like x86_64 or x86_64-v2. It is a variant of the x86_64 architecture, which is the most widely used instruction set for 64-bit processors in both personal computers and servers. The x86_64-v3 variant introduces improvements in instruction sets and CPU features that help optimize software for specific microarchitectures, such as Intel’s Skylake or AMD’s Zen processors.

Core Differences with Other Variants |

|

|

|

In essence, x86_64-v3 takes advantage of newer processor capabilities, resulting in improved performance for workloads that require high processing power.

Photo by admingeek from Infotechys

Understanding the x86_64 Architecture

To fully grasp what x86_64-v3 brings to the table, it’s essential to first understand the basics of the x86_64 architecture. The x86_64 architecture is the 64-bit extension of the x86 instruction set, developed by Intel and AMD. It allows systems to handle larger amounts of memory (up to 18.4 million terabytes) and process data in wider chunks, resulting in faster computation and better performance for high-demand applications.

Key Features of x86_64 |

|

|

|

While the base x86_64 architecture has these features, x86_64-v3 builds upon them, adding support for specific advanced instruction sets.

Key Features of x86_64-v3 architecture

The x86_64-v3 architecture introduces a series of optimizations, including but not limited to:

|

|

|

|

Differences Between x86_64, x86_64-v2, and x86_64-v3

Here’s a quick breakdown of the differences between the x86_64 architecture and its optimized variants:

| Feature | x86_64 | x86_64-v2 | x86_64-v3 |

|---|---|---|---|

| SIMD Support | SSE, SSE2 | AVX, AVX2 | AVX-512, FMA, etc. |

| Branch Prediction | Standard | Improved | Advanced |

| Memory Handling | Standard | Optimized for speed | Optimized for high throughput |

| Multithreading | Basic Support | Enhanced for Multi-core | Advanced Multi-threading Support |

| Compatibility | Broad | Broad | Requires specific CPU generations |

Benefits of Using x86_64-v3 |

By adopting x86_64-v3, developers can take advantage of several key performance enhancements:

|

|

|

For developers, this means faster execution of tasks, especially for workloads that benefit from modern SIMD operations or that require handling a large number of threads.

How to Enable x86_64-v3 for Your Applications

Enabling x86_64-v3 depends on the toolchain and compiler you are using. Below are instructions for two common scenarios:

For GCC |

gcc -march=x86-64-v3 -o my_application my_application.cFor Clang |

clang -march=x86-64-v3 -o my_application my_application.cEnabling Optimizations in CMake |

If you’re using CMake, you can specify the architecture optimization flag as follows:

set(CMAKE_CXX_FLAGS "${CMAKE_CXX_FLAGS} -march=x86-64-v3")Verify CPU Support |

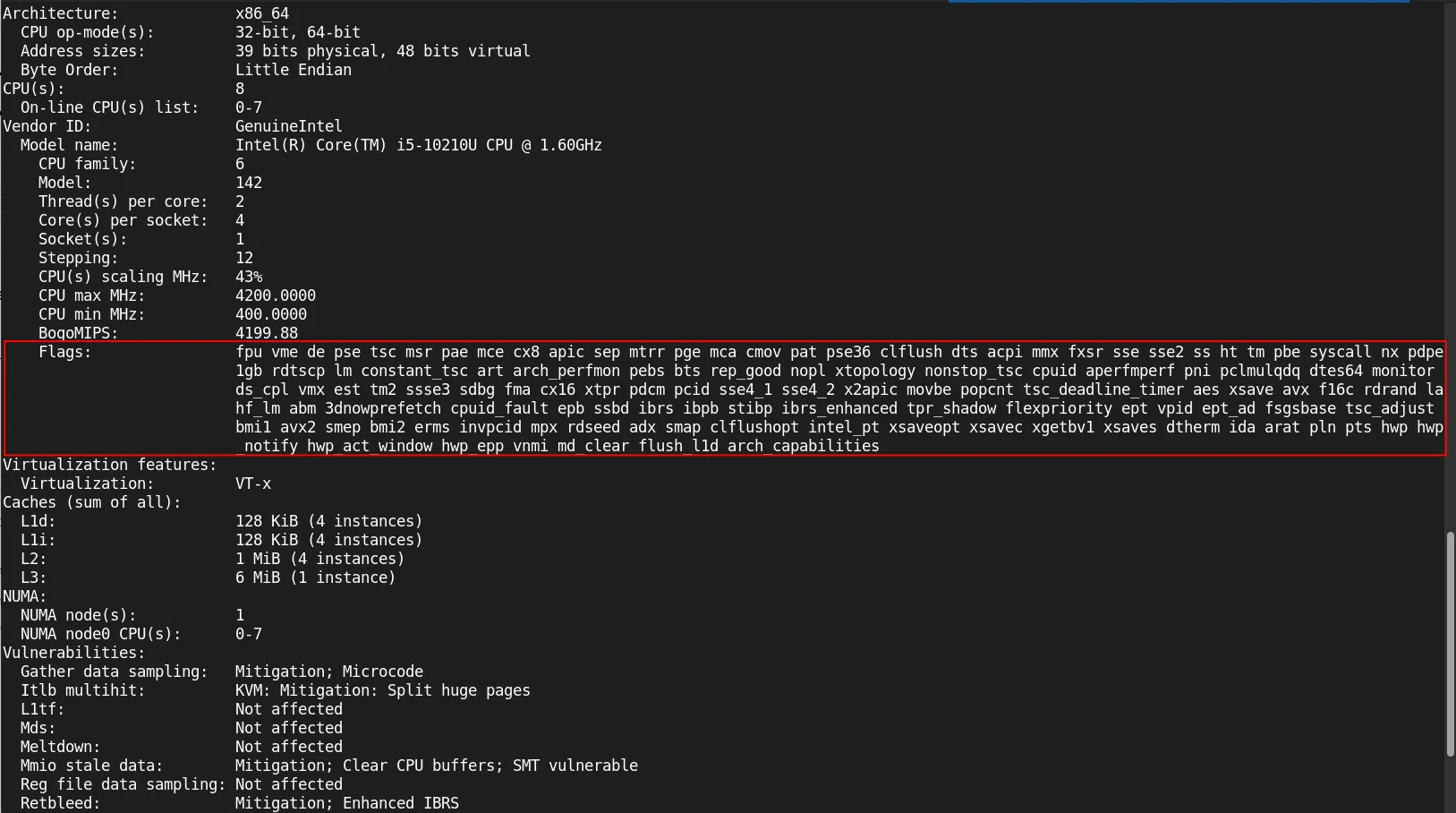

You can check if your processor supports x86_64-v3 by running:

lscpu

Photo by admingeek from Infotechys

This will display the supported CPU features. If your CPU supports AVX-512 or other advanced instructions, you’re ready to use x86_64-v3! Based on the CPU flags (highlighted in red), the image above shows an example of a CPU that does not support the x86_64-v3 architecture.

CPU Flag Descriptions |

This table provides a high-level overview of the various CPU flags and their functions.

| Flag | Description |

|---|---|

| fpu | Floating-point unit support |

| vme | Virtual mode extension |

| de | Debugging extension |

| pse | Page size extension |

| tsc | Time stamp counter |

| msr | Model-specific register support |

| pae | Physical address extension |

| mce | Machine check exception |

| cx8 | CMPXCHG8 instruction support |

| apic | Advanced programmable interrupt controller support |

| sep | Sysenter/Sysexit support |

| mtrr | Memory type range register support |

| pge | Page global enable |

| mca | Machine check architecture support |

| cmov | Conditional move instructions support |

| pat | Page attribute table support |

| pse36 | 36-bit page size extension |

| clflush | Cache line flush support |

| dts | Digital temperature sensor |

| acpi | Advanced configuration and power interface support |

| mmx | MMX technology support |

| fxsr | Fast floating-point extensions |

| sse | Streaming SIMD extensions support |

| sse2 | Streaming SIMD extensions 2 support |

| ss | Self-snoop support |

| ht | Hyper-threading support |

| tm | Thermal monitor support |

| pbe | Pending break event support |

| syscall | Fast system call support |

| nx | No execute bit support |

| pdpe | 64-bit page table extension |

| 1gb | 1GB pages support |

| rdtscp | Read time-stamp counter and processor ID |

| lm | Long mode (64-bit mode) support |

| constant_tsc | Constant time-stamp counter support |

| art | AMD reduced latency time-stamp counter |

| arch_perfmon | Architecture performance monitoring support |

| pebs | Precise event-based sampling support |

| bts | Branch trace store support |

| rep_good | REP string optimization |

| nopl | No operation instruction support |

| xtopology | Extended topology information |

| nonstop_tsc | Non-stop time-stamp counter support |

| cpuid | CPUID instruction support |

| aperfmperf | Architectural performance monitoring support |

| pni | Prescott new instructions (SSE3) support |

| pclmulqdq | PCLMULQDQ instruction support (carry-less multiplication) |

| dtes64 | 64-bit debug store support |

| monitor | MONITOR/MWAIT support |

| ds_cpl | Debug store with CPL (current privilege level) support |

| vmx | Virtualization extensions (Intel VT-x) support |

| est | Enhanced speedstep technology support |

| tm2 | Thermal monitor 2 support |

| ssse3 | Supplemental SSE3 support |

| sdbg | Silicon debug support |

| fma | Fused multiply-add instruction support |

| cx16 | CMPXCHG16B instruction support |

| xtpr | xTPR update notification support |

| pdcm | Processor data collection monitor support |

| pcid | Process-context identifiers support |

| sse4_1 | SSE4.1 instruction set support |

| sse4_2 | SSE4.2 instruction set support |

| x2apic | 2nd generation Advanced Programmable Interrupt Controller support |

| movbe | MOVBE instruction support (byte swap) |

| popcnt | POPCNT instruction support (population count) |

| tsc_deadline_timer | TSC deadline timer support |

| aes | AES encryption instruction support |

| xsave | XSAVE instruction support (extended state save) |

| avx | Advanced vector extensions support |

| f16c | 16-bit floating-point conversion support |

| rdrand | Random number generator instruction support |

| la | Legacy atomics |

| hf_lm | Hardware lock elision support (in hardware) |

| abm | Advanced bit manipulation support |

| 3dnowprefetch | 3DNow! prefetch support |

| cpuid_fault | CPUID fault handling support |

| epb | Enhanced performance boost support |

| ssbd | Speculative store bypass disable support |

| ibrs | Indirect branch restricted speculation support |

| ibpb | Indirect branch prediction barrier support |

| stibp | Store-indirect branch prediction barrier support |

| ibrs_enhanced | Enhanced indirect branch restricted speculation support |

| tpr_shadow | Task priority register shadowing support |

| flexpriority | Flexible priority model support |

| ept | Extended page tables support (Intel VT-x) |

| vpid | Virtual processor identifier support (Intel VT-x) |

| ept_ad | Extended page tables with access disable support |

| fsgsbase | FS/GS base access support |

| tsc_adjust | Time-stamp counter adjustment support |

| bmi1 | Bit manipulation instructions 1 support |

| avx2 | Advanced vector extensions 2 support |

| smep | Supervisor mode execution protection support |

| bmi2 | Bit manipulation instructions 2 support |

| erms | Enhanced REP MOVSB/STOSB support (faster memory operations) |

| invpcid | Invalidate process-context identifier support |

| mpx | Memory protection extensions (Intel) support |

| rdseed | RDSEED instruction support (hardware random number generation) |

| adx | ADCX/ADOX instructions support |

| smap | Supervisor mode access prevention support |

| clflushopt | CLFLUSHOPT instruction support |

| intel_pt | Intel processor trace support |

| xsaveopt | Optimized XSAVE instruction support |

| xsavec | XSAVE legacy compression support |

| xgetbv1 | XGETBV instruction (read extended control register) support |

| xsaves | XSAVES instruction support (extended state save) |

| dtherm | Digital thermal sensor support |

| ida | Intel dynamic acceleration (ID) support |

| arat | Always running APIC timer support |

| pln | Processor logic node support |

| pts | Processor time-stamp support |

| hwp | Hardware controlled performance (Intel HWP) support |

| hwp_notify | Hardware performance notification support |

| hwp_act_window | Hardware active window for power management |

| hwp_epp | Hardware energy performance preference support |

| vnmi | Virtual NMI support |

| md_clear | Memory device clear support |

| flush_l1d | Flush L1 data cache support |

| arch_capabilities | Architecture-specific capabilities support |

Real-World Use Cases for x86_64-v3

x86_64-v3 is particularly beneficial in scenarios requiring high performance, including:

|

|

|

|

FAQ

What is the difference between x86_64 and x86_64-v3? |

x86_64-v3 is an optimized version of the standard x86_64 architecture, offering better performance through new instruction sets, improved memory handling, and enhanced multi-core processing.

How can I know if my CPU supports x86_64-v3? |

You can check your CPU’s supported features using the lscpu command in Linux or check your processor’s specifications on the manufacturer’s website.

Should I always use x86_64-v3 for my application? |

If your target audience uses processors that support x86_64-v3 (e.g., Intel Cascade Lake, Ice Lake or AMD EPYC), then yes. Otherwise, for broader compatibility, you may want to stick with x86_64 or x86_64-v2.

No comments:

Post a Comment